Дешифраторы и шифраторы

Из микросхем комбинационного типа при разработке цифровых устройств широко используют дешифраторы, их номенклатура довольно разнообразна.

Микросхема ИДЗ (рис. 79) имеет четыре адресных входа 1, 2,4, 8, два инверсных входа стробирования S, объединенных по И, и 16 ёвыходов 0-15 Если на обоих входах стробирования лог. 0, на том из выходов, номер которого соответствует десятичному эквиваленту входного кода (вход 1 - младший разряд, вход 8 -старший), будет лог. 0, на остальных выходах - лог. 1. Если хотя бы на одном из входов стробирования S лог. 1, то независимо от состояний входов на всех выходах микросхемы формируется лог. 1.

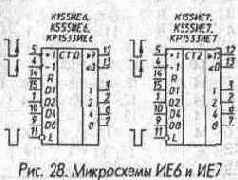

Наличие двух входов стробирования существенно расширяет возможности использования микросхем. Из двух микросхем ИДЗ, дополненных одним инвертором, можно собрать дешифратор на 32 выхода (рис. 80), де-

шифратор на 64 выхода собирается из четырех микросхем ИДЗ и двух инверторов (рис 81), а на 256 выходов - из 17 микросхем ИДЗ (рис 82)

Микросхема ИД4 (рис 83) содержит два дешифратора на четыре выхода каждый с объединенными адресными входами и разделенными входами стробирования Лог 0 на выходах первого (верхнего по

схеме) дешифратора формируется (аналогично ИДЗ) лишь при наличии на обоих стробирующих входах лог 0 .Соответствующее условие для второго дешифратора - наличие на одном из его входов стробирования лог 1 (вывод 1), а на другом - лог 0 (вывод 2). Такая структура микросхемы позволяет использовать ее в различных вариантах включения. На основе микросхемы ИД4 могут быть построены, в частности, дешифраторы на восемь выходов со входом стробирования (рис 84) и на 16 выходов (рис 85). На девяти микросхемах

ИД4 можно собрать дешифратор на 64 выхода по схеме, подобной рис. 82. Если дополнить микросхему ИД4 тремя элементами 2И-НЕ, можно получить дешифратор на десять выходов (рис. 86).

Микросхема К555ИД5 (рис. 83) аналогична по функционированию ИД4, но имеет выходы с открытым коллектором.

Описанные двоичные дешифраторы являются полными: любому состоянию адресных входов соответствует нулевое состояние некоторого единственного выхода.

В ряде случаев, например при двоично-десятичном представлении чисел, удобно использовать неполные дешифра-

торы, в которых число выходов меньше числа возможных состояний адресных входов. В частности, двоично-десятичный дешифратор содержит десять выходов и не меньше четырех входов. На основе полного дешифратора всегда можно построить неполный на меньшее число входов.

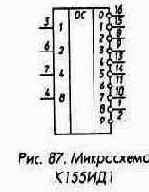

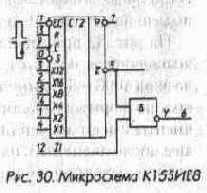

Однако ввиду широкого использования в устройствах индикации двоично-десятичных дешифраторов в состав серии К 155 специально включен двоично-десятичный дешифратор К155ИД1 с высоковольтным выходом (рис. 87). Дешифратор имеет четыре входа, которые могут подключаться к выходам любого источника кода 1-2-4-8, и десять выходов, которые могут подключаться к катодам газоразрядного цифрового или знакового индикатора

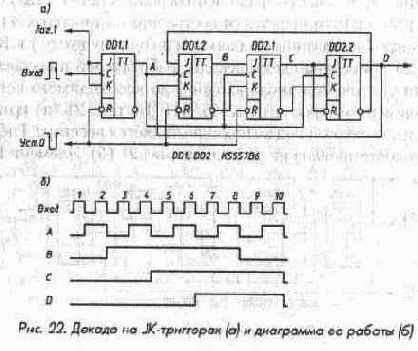

(анод последнего через резистор сопротивлением 22...91 кОм подключен к полюсу источника постоянного или пульсирующего напряжения 200...300 В). Схема подключения дешифратора к микросхеме К155ИЕ4, включенной в режим деления на 10 с кодом 1-2-4-6, приведена на рис. 88. Для подключения микросхемы К155ИД1 к выходам декады на микросхемах ТМ2 (см. рис. 19) или декады по рис. 22 необходим дополнительный элемент И, в качестве которого могут быть использованы два любых маломощных диода (рис. 89) или 1/4 часть интегральной микросхемы ЛИ1. Для подключения выходов микросхемы К155ИД1 ко входам других микросхем ТТЛ следует принять дополнительные меры по согласованию уровней, поскольку техническими условиями на микросхему К155ИД1 гарантируется выходное напряжение в состоянии лог. 0 не более 2,5 В, что превышает порог переключения микросхем ТТЛ, составляющий около 1,3 В. Практически выходное напряжение микросхем К155ИД1 в состоянии 0 может быть несколько выше или ниже порога пере-

ключения, поэтому для надежной работы микросхемы-нагрузки в минусовую цепь питания этой микросхемы следует включить кремниевый диод. Такое включение повысит порог переключения примерно до 2 В, что обеспечит ее согласование с дешифратором К155ИД1.

Кроме того, поднимется выходной уровень лог. 0 микросхемы примерно до 0,9 В, что вполне достаточно для нормальной работы последующих микросхем. На рис. 90 приведена схема делителя частоты на 10 с переключаемой в пределах 10...1,1 скважностью выходных импульсов, иллюстрирующая описанные выше правила согласования дешифратора К155ИД1 с микросхемами ТТЛ. Микросхема К555ИД6 (рис. 91) - неполный дешифратор двоично-десятичного кода 1-2-4-8. Как и микросхема К155ИД1, она имеет четыре адресных входа 1,2,4,8, но ее десять выходов 0-9 выполнены

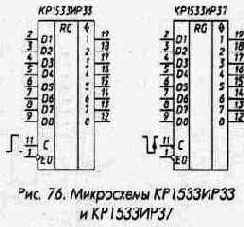

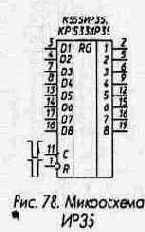

по стандартной схеме. При подаче на входы 1, 2 4,8 кода чисел 0-9 на том выходе, номер которого соответствует десятичному эквиваленту входного кода, появляется лог. 0, на остальных выходах -лог. 1: при входных кодах, соответствующих числам 10-15, на всех выходах - лог. 1. Микросхема ИД7 (рис. 92) - дешифратор, имеющий три адресных входа 1,2,4, три входа стробирования S, два из которых инверсные, и восемь инверсных выходов. Лог. 0 на одном из выходов может появиться лишь при единственном разрешающем сочетании сигналов на входах стробирования S - на инверсных входах должен быть лог. 0, на прямом - лог. 1. При всех других сочетаниях сигналов на входах S на всех выходах микросхемы -лог. 1. Сигнал лог. 0 при разрешающем сочетании на входах появится на том выходе дешифратора, номер которого соответствует десятичному эквиваленту кода, поданному на адресные входы 1, 2, 4.

Наличие трех входов стробирования позволяет простыми средствами объединять микросхемы для наращивания разрядности дешифратора. Три микросхемы ИД7 можно объединить в дешифратор на 24 выхода без дополнительных элементов (соединение микросхем DD1 -DD3 на рис. 93), четыре микросхемы и инвертор - в дешифратор на 32 выхода (рис. 93). Дополнив схему рис. 93 еще четырьмя микросхемами ИД7 и инвертором, можно получить дешифратор на 64 выхода. Микросхема ИД10 (рис. 94) - дешифратор, по функционированию соответствующий микросхеме К555ИД6, но с выходами, выполненными с открытым коллектооом.

Для микросхемы К555ИЛ10

в состоянии лог. 0 ее выходной ток может достигать 24 мА, в состоянии лог. 1 на ее выход можно подавать напряжение до 15 В. Для микросхемы К155ИД10 максимально допустимое напряжение, которое можно подвести к выходу, находящемуся в состоянии лог. 1, также составляет 15 В. Выходное напряжение лог. 0 при втекающем токе 20 мА не более 0,4 В, при токе 80 мА - не более 0,9 В. Указанные выходные параметры позволяют применять микросхему К155ИД10 при построении распределителей с релейными выходами (рис. 95).

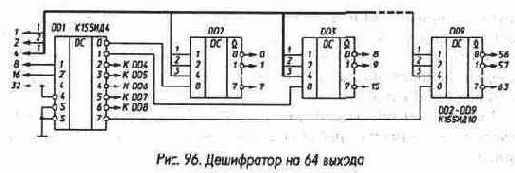

При необходимости увеличения числа выходов стробирование микросхемы можно осуществлять по входу 8. Для примера на рис. 96 приведена схема дешифратора на 64 выхода. Отметим, что в соответствии с рис. 96 можно при необходимости соединять микросхемы К155ИД1, К555ИД6. Микросхема КР531ИД14 (рис. 97) содержит два стробируемых дешифратора, каждый с двумя адресными входами 1 и 2, инверсным

входом стробирования S и инверсными выходами 0-3. Как и в других дешифраторах ТТЛ-серий, при разрешающем лог. 0 на входе S лог. 0 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту двоичного числа, поданному на адресные входы 1 и 2. При лог. 1 на входе S на всех выходах дешифратора также лог. 1. Для получения дешифраторов с большим числом выходов можно соединять микросхемы в соответствии с рис. 98.

Функцию, обратную функции дешифраторов, выполняют шифраторы. Микросхема ИВ1 - приоритетный шифратор (рис. 99). Она имеет восемь информационных входов 0-7 и вход разрешения Е. Выходов у микросхемы пять - три инверсных выходного кода 1,2,4; G -признака подачи входного сигнала и Р - переноса. Если на всех информационных входах микросхемы лог. 1, на выходах 1,2,4, G - лог. 1, на выходе Р - лог. 0. При подаче лог. 0 на любой из информационных входов 0-7 на выходах 1,2, 4 появится инверсный код, соответствующий номеру входа, на который подан лог. 0, на выходе G'- лог. 0, что

является признаком подачи входного сигнала, на выходе Р - лог. 1, которая запрещает работу других микросхем ИВ1 при их каскадном соединении.

Если лог. 0 будет подан на несколько информационных входов микросхемы, выходной код будет соответствовать входу с большим номером. Так работает микросхема при подаче на вход Е лог. 0. Если же на входе Е лог. 1 (запрет работы), на всех шести выходах микросхемы лог. 1.

Две микросхемы ИВ1 можно соединить по схеме рис. 100 для получения приоритетного шифратора на 16 входов. Если лог. 0 подан на один из входов 0-7, на выходах DD3 появятся младшие разряды прямого выходного кода, на выходе G DD1 - лог. 0, определяющий разряд 8 выходного кода, на выходе Р - лог. 1, являющаяся признаком подачи входного сигнала. Если лог. 0 подать на один из входов 8-15, лог. 1 с выхода Р DD2 запретит работу DD1, младшие разряды на выходах DD3 определяются микросхемой DD2, на выходе 8 выходного кода будет лог. 1. Таким образом, с выходов 1,2,4,8 устройства по схеме рис. 100 можно снять прямой код, соответствующий номеру входа, на который подан лог. 0. Микросхемы ИВ1 можно соединять для получения большего числа входов. В этом случае выходы переноса микросхем с большими номерами следует соединить со входами запрета микросхем с меньшими номерами, выходы 1, 2,4 следует через многовходовые элементы И-НЕ подключить к выходам устройства - это будут младшие разряды выходного кода. Выходы G микросхем ИВ1 следует соединить с входами 0-7 еще одной микросхемы ИВ1, с выходов которой можно будет снять старшие разряды кода и признак подачи входного сигнала G (рис. 101). В схемах рис. 100 и 101 сохраняется свойство приоритетности шифраторов - при одновременной подаче лог. 0 на несколько входов выходной код всегда соответствует входу с наибольшим номером.

Микросхема К555ИВЗ (рис. 102) - приоритетный шифратор. Она имеет девять инверсных входов 1-9 для подачи кодируемого сигнала и четыре инверсных выхода кода 1-2-4-8. В исходном состоянии на всех входах и выходах лог. 1. При подаче на любой из входов лог. 0 на выходах 1-2-4-8 формируется инверсный код номера входа, на который подан лог. 0. Если лог. 0 подан сразу на несколько входов, код на выходе соответствует наибольшему номеру входа, на который подан лог. 0.

Основное назначение микросхемы - преобразование номера источника сигнала в код, например номера нажатой кнопки. Для примера на рис. 103 показана схема квазисенсорного переключателя на 10 положений, выходными сигналами которого является код 1-2-4-8 нажатой и отпущенной кнопки (аналог переключателя с взаимовыключением). При включении питания все триггеры микросхемы DD2 устанавливаются в 0, на выходах 1-2-4-8 код 1111, не соответствующий ни одной из нажатых кнопок. Если нажать любую из 10 кнопок SB1 - SB10, на выходе микросхемы DD1 сформируется инверсный код нажатой кнопки (для кнопки SB1 - 1111), этот код поступит на информационные входы микросхемы DD2. Ток через один из резисторов R1 - R10, соответствующий нажатой кнопке, включит транзистор VT1, на его коллекторе появится лог. 0 на время нажатия кнопки. Напряжение на левой обкладке конденсатора С2 начнет уменьшаться и через время,

в течение которого прекратится дребезг контактов кнопки, достигнет порога переключения элемента DD3.1. На выходе элемента DD3.1 появится лог. 1, на выходе DD3.2 - лог. 0. Изменение напряжения на правой обкладке конденсатора передается на вход элемента DD3.1, в результате чего произойдет скачкообразное переключение элементов микросхемы DD3 в противоположное состояние (рис. 104). Изменение лог. 0 на выходе элемента DD3.3 на лог. 1 приведет к записи инверсного кода с выходов микросхемы DD1 в триггеры микросхемы DD2, на ее инверсных выходах появится прямой код нажатой кнопки. В момент отпускания кнопки первое размыкание ее контактов приведет к появлению лог. 1 на нижнем по схеме входе элемента DD3.1, вся цепочка элементов микросхемы DD3 переключится. На время дребезга контактов кнопки лог. 1 на верхнем по схеме входе элемента DD3,1 будет поддерживаться за счет положительной обратной связи через конденсатор С2. На выходе микросхемы DD2 сохранится код нажатой кнопки,. Если при нажатой кнопке нажать еще одну, выходной код не изменится, он будет соответствовать первой из нажатых кнопок. Код не изменится и при отпускании кнопок.Если нажать одновременно (с точностью до задержки, вносимой цепью подавления дребезга DD3.1, DD3.2) две или более кнопок, выходной код будет соответствовать кнопке с большим номером.

В схеме рис. 103 можно использовать и микросхему (несколько микросхем) ИВ1, в этом случае транзистор VT1 излишен. Входной сигнал на схему подавления дребезга необходимо будет подать с выхода G микросхемы ИВ1.

Микросхемы серии ТТЛ

Глава 1.Микросхемы серии ТТЛ.

1.1 Общие сведения. 1.2 Микросхемы комбинационного типа малой степени интеграции. 1.3 Микросхемы последовательстного типа. 1.4 Микросхемы комбинационного типа средней степени интеграции. 1.5 Ждущие мультивибраторы и генераторы.Микросхемы комбинационного типа малой степени интеграции

Существует много типов микросхем ТТЛ малой степени интеграции, различающихся по функциональному назначению, нагрузочной способности, схеме выходного каскада. Работа логических элементов этих микросхем достаточно проста. Для элементов И выходной уровень лог. 1 формируется при подаче на все входы элемента уровней лог. 1, для элемента ИЛИ для формирования уровня лог. 1 на выходе достаточно подачи хотя бы на один вход уровня лог. 1. Элементы И-НЕ (основной элемент серий ТТЛ) и ИЛИ-НЕ дополнительно инвертируют выходной сигнал, элемент И-ИЛИ-НЕ состоит из нескольких элементов И, выходы которых подключены к входам элемента ИЛИ-НЕ.

По нагрузочной способности микросхемы можно разделить на стандартные (№10 для серий К 155 и КР531 и N = 20 и 40 для микросхем серий К555 и КР1533 соответственно), микросхемы с повышенной нагрузочной способностью (N = 30 и более), микросхемы со специальным выходным каскадом, обеспечивающим значительно более высокую нагрузочную способность в одном из логических состояний. Некоторые типы микросхем выпускают с так называемым «открытым» коллекторным выходом.

Отдельно следует отметить специальный класс микросхем с третьим состоянием выходного каскада, называемым также еще «высокоимпедансным», или «Z-состоянием», при котором микросхема отключается по своему выходу от нагрузки. Это, как правило, буферные элементы с относительно большой нагрузочной способностью.

На рис. 2 приведены графические обозначения микросхем ТТЛ, выполняющих функции И-НЕ - самой многочисленной группы простых логических микросхем.

Микросхемы ЛА1 - ЛА4 имеют стандартную для своей серии нагрузочную способность, микросхемы ЛА6 и ЛА12 всех серий, КР1533ЛА21 - КР1533ЛА24 - втрое большую (здесь и далее в тексте в названии оставлена только та его часть, которая определяет тип триггера, счетчика, логического элемента и т. п., если такие же обозначения используются в микросхемах нескольких серий).

Микросхемы ЛА7 - ЛА11, ЛА13, КР1533ЛА23 выполнены с открытым коллектором, нагрузочная способность для ЛА7- ЛА11 в состоянии лог. 0 стандартная, для ЛА13 и КР1533ЛА23 - втрое большая.

Максимально допустимое напряжение, которое можно подавать на выход микросхемы ЛА11, находящейся в состоянии лог. 1, - 12 В, для остальных - 5,5 В. Микросхема КР531ЛА16 (рис. 2) - два мощных магистральных усилителя, выполняющих функцию 4И-НЕ. Нагрузочная способность каждого усилителя 60 мА в состоянии лог. 0 и 40 мА в состоянии лог. 1 при выходном напряжении 2 В, что позволяет работать на линию связи с волновым сопротивлением 50 Ом, нагруженную на конце. Кроме того, гарантируется, что при выходном напряжении 2,7 В в состоянии лог. 1 выходной ток составляет не менее 3 мА. Микросхема КР531ЛА17 (рис. 2) - два элемента 4И-НЕ с возможностью перевода выхода в высокоимпедансное состояние при подаче на вход Е лог. 1. При подаче на вход Е лог. 0 выходы активны, допустимые выходные токи составляют 50 мА в состоянии лог. 0 и 32 мА в состоянии лог. 1 при выходном напряжении 2 В, что обеспечивает возможность работы на линию связи с волновым сопротивлением 75 Ом. Дополнительно гарантируется, что при выходном напряжении 2,7 В в состоянии лог. 1 выходной ток составляет не менее 3 мА. Входные токи микросхем КР531ЛА12, КР531ЛА13, КР531ЛА16, КР531ЛА17 по сигнальным входам в состоянии лог. 0-4 мА, по входам Е - 2 мА. Микросхема К155ЛА18 (рис. 2) выполнена с открытым коллектором, ее выходное напряжение в состоянии лог. 0 не более 0,5 В при выходном втекающем токе 100 мА и не более 0,8 В при токе 300 мА. Максимальное напряжение на выходе в состоянии лог. 1 — 30 В, что позволяет коммутировать нагрузку мощностью до 9 Вт - электромагнитные реле, маломощные электродвигатели. Лампы накаливания, однако, можно использовать на номинальный ток не более 60 мА, так как сопротивление нити лампы в холодном состоянии значительно меньше номинального. Микросхема КР531ЛА19 (рис. 2) - двенадцативходовый элемент И-НЕ с возможностью перевода выхода в высокоимпедансное состояние при подаче лог. 1 на вход Е. В состоянии лог. 1 при выходном напряжении 2,4 В микросхема допускает выходной ток до 6,5 мА, в состоянии лог. 0-20 мА. Микросхема К155ЛП7 (рис. 2) - два стандартных логических элемента И-НЕ с двумя объединенными входами и два n-р-n транзистора с предельно допустимым коллекторным напряжением 30 В и максимальным током коллектора 300 мА.

Подложка микросхемы подключена к выводу 8, что позволяет, подключив ее к источнику отрицательного напряжения, коммутировать транзистором и отрицательные сигналы, не выходящие по амплитуде за напряжение этого источника.

На рис. 3 приведены графические обозначения микросхем, выполняющих функцию ИЛИ-НЕ. На входах микросхем К155ЛЕ2, К155ЛЕЗ установлены дополнительные элементы И, позволяющие стробировать входные сигналы. Нагрузочная способность микросхем ЛЕ1 - ЛЕ4, КР531ЛЕ7 стандартная для соответствующей серии, микросхем К155ЛЕ5 и К155ЛЕ6 в состоянии лог. 0-48 мА, что соответствует N = 30, в состоянии лог. 1 - выше. Микросхема К155ЛЕ5 может обеспечить при выходном напряжении 2,4 В вытекающий ток 2,4 мА, микросхема К155ЛЕ6 - 13,2 мА. Для микросхемы К155ЛЕ6

нормирован также ток при выходном напряжении 2 В - он составляет не менее 42,4 мА, то есть эта микросхема может обеспечивать работу на нагрузку 50 Ом, например, на коаксиальный кабель с волновым сопротивлением 50 или 75 Ом, согласованный на конце. Микросхемы КР1533ЛЕ10 и КР1533ЛЕ11 имеют нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема КР1533ЛЕ11 выполнена с открытым коллектором, максимальное напряжение, которое можно подать на ее выход в закрытом состоянии, - 5,5 В. На рис. 4 приведены графические обозначения микросхем, выполняющих функцию И. Микросхемы ЛИ1, ЛИЗ, ЛИ6 имеют стандартную для своих серий нагрузочную способность, микросхемы ЛИ2

и ЛИ4 выполнены с открытым коллектором, их нагрузочная способность в состоянии лог. 0 стандартная, в состоянии лог. 1 допускается подача напряжения 5,5 В. Микросхема К155ЛИ5 выполнена с открытым коллектором, ее нагрузочная способность такая же, как у К155ЛА18.

Микросхемы КР1533ЛИ8 и КР1533ЛИ10 имеют нагрузочную способность втрое большую стандартной для микросхем этой серии. На рис. 5 приведены графические обозначения микросхем, выполняющих функцию ИЛИ. Микросхема ЛЛ1 имеет стандартную нагрузочную способность, микросхема К155ЛЛ2 выполнена с открытым коллектором и имеет нагрузочную способность такую же, как К155ЛА18. Микросхема КР1533ЛЛ4 имеет нагрузоч ную способность втрое большую стандартной для микросхем этой серии На рис. 6 приведены графические обозначения микросхем, выполняющих функцию НЕ (инверторы).

Микросхемы ЛН1 имеют стандартную нагрузочную способность, а ЛН2, К155ЛНЗ, К155ЛН5 выполнены с открытым коллектором и имеют стандартную нагрузочную способность в состоянии лог. 0. Для К155ЛНЗ и К155ЛН5 дополнительно гарантируется, что при втекающем токе 40 мА выходное напряжение в состоянии лог. 0 не превышает 0,7 В. Допустимое напряжение на выходе микросхемы в состоянии лог. 1 составляет 5,5, 30 и 15 В для ЛН2, К155ЛНЗ и К155ЛН5 соответственно. Микросхема К155ЛН6 (рис. 6) - шесть мощных инверторов с возможностью перевода выходов в высокоимпедансное состояние. Управление состоянием выходов производится по двум равноправным входам управления Е (1 и 15), собранным по схеме, выполняющей функцию И. При подаче на оба указанных входа лог. 0 выходы инверторов переходят в активное состояние и инвертируют входные сигналы, при подаче хотя бы на один вход лог. 1 - переходят в высокоимпедансное состояние. Нагрузочная способность инверторов довольно велика - при лог. 0 на выходе выходной втекающий ток может достигать 32 мА, при этом выходное напряжение не более 0,4 В, при лог. 1 на выходе выходной вытекающий ток - до 5,2 мА при выходном напряжении 2,4 В. Микросхема КР1533ЛН7 (рис. 6) - шесть инверторов с повышенной нагрузочной способностью и возможностью перевода выходов в высокоимпедансное состояние. Инверторы объединены в две группы,

у каждой из которых свой вход управления. Подача лог. 0 на вход Е1 включает инверторы с выходами 1-4, на вход Е2 - с выходами 5 и 6. Нагрузочная способность микросхемы 12 мА при 0,4 В в состоянии лог. 0 и 3 мА при 2,4 В в состоянии лог. 1. Микросхема КР1533ЛН8 (рис. 6) - шесть инверторов с повышенной нагрузочной способностью; максимальный уровень в состоянии лог. 0 -0,4 В при втекающем токе 12 мА и 0,5 В при 24 мА, минимальный уровень в состоянии лог. 1 2,4 В при вытекающем токе 3,0 мА и 2,5 В при 0,4 мА. Микросхема КР1533ЛН10 имеет нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема выполнена с открытым коллектором, максимальное напряжение, которое можно подать на ее выход в закрытом состоянии - 5,5 В. На рис. 7 приведены графические обозначения микросхем, выполняющих функцию И-ИЛИ-НЕ и расширителей И-ИЛИ.

Все микросхемы И-ИЛИ-НЕ имеют стандартные выходы, кромеКР531ЛР10, которая выполнена с открытым коллектором, допустимое напряжение для нее в состоянии лог. 1 - 5,5 В. Следует отметить различие микросхем К155ЛР4 и К555ЛР4, КР1533ЛР4, а такжеК555ЛР11, КР1533ЛР11 и КР531ЛР11. Микросхемы К155ЛР1, К155ЛРЗ, К155ЛР4 имеют входы для подключения расширителей И-ИЛИ К155ЛД1 и К155ЛД2, увеличивающих число групп И в функции ИЛИ этих микросхем. Аналогичные входы для расширения числа входов по ИЛИ имеет микросхема К155ЛЕ2. Однако более простой способ построения элементов И или ИЛИ с большим числом входов - каскадное соединение микросхем,

выполняющих функции И-НЕ и ИЛИ-НЕ. На рис. 8 (а) приведена схема элемента И на 16 входов, на рис. 8 (б) - элемента ИЛИ на 32 входа. На рис. 8 (в) приведена схема элемента совпадения, формирующего на своем выходе лог. 1 при лог. 1 на четырех верхних по схеме входах и лог. 0 на трех нижних. Такой элемент может использоваться для дешифрации определенных состояний счетчиков и других устройств. На рис. 9 приведены графические обозначения микросхем - повторителей входного сигнала. Микросхема ЛП8 - четыре повторителя входного сигнала с высокоимпедансным состоянием. При лог. 0 на управляющем входе Е сигналы с входа D элемента проходят на выход элемента без инверсии. При лог. 1 на входе Е выход элемента переходит в высокоимпедансное состояние. При лог. 0 на выходе микросхема К155ЛП8 обеспечивает втекающий ток 16 мА, при лог. 1 - вытекающий 5,2 мА, К555ЛП8 - 24 мА и 2,6 мА соответственно. Микросхема К155ЛП9 (рис. 9) - шесть повторителей входного сигнала с открытым коллектором, ее выходные параметры такие же, как и у К155ЛНЗ. Микросхема К155ЛП10 (рис. 9) - шесть мощных повторителей с возможностью перевода выходов в высокоимпедансное состояние.

Логика управления и нагрузочная способность этой микросхемы такие же, как и у К155ЛН6. Микросхема К155ЛП11 (рис. 9) - шесть мощных повторителей, подобных повторителям микросхемы К155ЛП10, но разбитых на две группы, каждая из которых имеет свой вход управления.

Подача лог. 0 на вход Е1 включает повторители с выходами 1-4, вход Е2 управляет выходами 5 и 6. Нагрузочная способность микросхемы К155ЛП11 такая же, как у К155ЛН6. Микросхемы КР1533ЛП16 и КР1533ЛП17 имеют нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема КР1533ЛП17 выполнена с открытым коллектором,

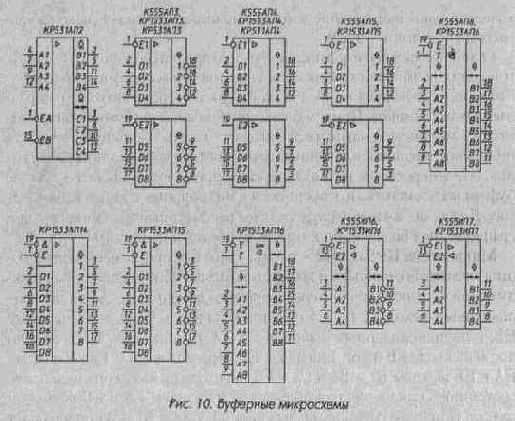

максимальное напряжение, которое можно подать на ее выход в закрытом состоянии - 5,5 В. Основное назначение микросхем-повторителей входного сигнала, имеющих возможность перевода выходов в высокоимпедансное состояние, - поочередная подача на одну магистраль сигналов от различных источников. Причем благодаря большой нагрузочной способности микросхем магистраль может иметь большую емкость и большое число подключенных к ней нагрузок и источников сигналов. Эти микросхемы находят широкое применение также в качестве буферных элементов, в особенности в микропроцессорных микросхемах. Для таких же целей служат далее рассматриваемые микросхемы, графические обозначения которых приведены на рис. 10. Микросхема КР531АП2 - четыре пары буферных неинвертирующих элементов с открытым коллектором, частично соединенных между собой. Сигналы могут передаваться со входов А1 - А4 на двунаправленные выходы С1 - С4 при лог. 0 на входе ЕА и лог 1 на входе ЕВ, с двунаправленных выводов С1 - С4 на выходы В1 - В4 при лог. 0 на входе ЕВ и лог. 1 на входе ЕА. При подаче лог. 1 на оба входа ЕА и ЕВ выходы В1 - В4 и С1 - С4 переходят в высокоимпедансное состояние. Одновременная подача лог. 0 на входе ЕА и ЕВ не допускается. Попарное соединение выводов А1 - А4 и В1 - В4 превращает микросхему в четыре двунаправленных ключа, максимальный выходной ток в состоянии лог. 0-60 мА, максимальные входное и выходное напряжения в состоянии лог. 1-10,5 В, входной ток в состоянии лог. 0 не превышает 0,15 мА. Микросхема АПЗ (рис. 10) - восемь инвертирующих буферных элементов с повышенной нагрузочной способностью и возможностью перевода выходов в высокоимпедансное состояние. Элементы разбиты на две группы по четыре, у каждой из групп свой вход управления для включения элементов и их перевода в третье состояние (Е1 и Е2).

Включение элементов каждой группы происходит при подаче на соответствующий вход (Е1 и Е2) лог. О, переход в высокоимпедансное состояние - при подаче лог. 1. Выходной втекающий ток микросхемы К555АПЗ в состоянии лог. О при напряжении на выходе 0,5 В может достигать 24 мА, вытекающий в состоянии лог. 1 при напряжении на выходе 2 В - 15 мА. Для микросхем КР1533АПЗ максимальный уровень лог. 0 0,4 В при втекающем токе 12 мА и 0,5 В при 24 мА. Минимальный уровень лог. 1 2,4 В при вытекающем токе 3 мА и 2,5 В при 0,4 мА. Нагрузочная способность микросхемы КР531АПЗ в состоянии лог. 0 64 мА, в состоянии лог. 1 3 мА при выходном

напряжении 2,4 В и 15 мА при 2 В. Входные токи по сигнальным входам D1 - D8 в состоянии лог. 0 0,4 мА. Микросхема АП4 (рис. 10) - восемь аналогичных буферных элементов без инверсии. Отличие ее в том, что один из входов включения элементов и их перевода в третье состояние (El) - инверсный, подобно АПЗ, второй (Е2) - прямой. Нагрузочная способность этой микросхемы такая же, как у АПЗ. Микросхема АП5 (рис. 10) - восемь неинвертирующих буферных элементов, обе группы которых имеют инверсные входы управления включением. В остальном эта микросхема аналогична АП4. Микросхемы АПЗ - АП5 служат для буферизации и коммутации сигналов в микропроцессорных устройствах, например, сигналов адреса, сигналов управления при организации внутренних и внешних шин микро-ЭВМ. Основное их назначение - обеспечение однонаправленной передачи информации. Однако при необходимости с их помощью можно обеспечить и двунаправленную передачу. На рис. 11 в качестве примера показано соединение выводов микросхемы АП4 для получения двунаправленного буферного элемента. При подаче лог. 0 на объединенные между собой входы Е1 и Е2 происходит передача сигнала от расположенных слева по рисунку выводов микросхемы (входы А1 -А4) к правым (В1 - В4), при подаче лог. 1 - наоборот: от В1 - В4 к А1 -А4. Два треугольника в среднем поле графического обозначения микросхемы символизируют усиление и направление передачи сигнала, верхний - при подаче активного сигнала на вход Е1 (для инверсного входа - лог. 0), нижний - на вход Е2 (для прямого входа - лог. 1).

Интересно отметить, что расположение информационных входов и выходов микросхем АПЗ - АП5 сделано специально такое, как показано на рис. 11, - для удобного их соединения. Однако для организации двунаправленной передачи информации удобнее использовать специально предназначенные для этой цели микросхемы, описываемые далее. Микросхема АП6 (см. рис. 10) - восемь двунаправленных неинвертирующих буферных элементов. Кроме двух групп информационных выводов А1 - А8 и В1 - В8, микросхема имеет два входа управления - Е и Т. Сигнал лог. 0, подаваемый на вход Е, разрешает включение буферных элементов, лог. 1 - переводит все выводы микросхемы в Z-состояние. Сигнал на входе Т действует при лог. 0 на входе Е и определяет направление передачи сигналов - при лог. 1 на входе Т выводы А1 - А8 являются входами, В1 - В8 - выходами, при лог. 0 - наоборот; В1 - В8 - входы, А1 - А8 - выходы. Два треугольника у входа Т символизируют усиление и направление распространения сигнала, верхний - при лог. 1 на входе Т, нижний - при лог. 0. Микросхема АП6 по своему функционированию (но, к сожалению, не по разводке выводов) соответствует микросхеме КР580ВА86, но потребляет в 1,7 раза меньшую мощность (К555АП6). Микросхема КР1533АП14 (рис. 10) содержит восемь однонаправленных буферных элементов с возможностью перевода их выходов в высокоимпедансное состояние. При подаче на оба входа разрешения Е лог. 0 выходы микросхемы переходят в активное состояние и на них появляются без инверсии сигналы с соответствующих входов D1 - D8. При поступлении на любой из входов Е лог. 1 выходы переходят в высокоимпедансное состояние. Микросхема КР1533АП15 (рис. 10) аналогична микросхеме КР1533АП14, только она инвертирует входные сигналы. Микросхема КР1533АП16 (рис. 10) состоит из восьми двунаправленных буферных элементов и, в основном, аналогична микросхеме КР1533АП6. Она инвертирует сигналы при передаче их с выводов А на выводы В и не инвертирует их при передаче в обратном направлении. На графическом изображении микросхемы КР1533АП16 для отражения этого свойства у вывода Т, определяющего направление передачи информации, верхний треугольник, символизирующий передачу сигналов с выводов А на выводы В при подаче на вход Т лог. 1, дополнен кружком инверсии, а нижний треугольник (на входе Т - лог. 0) показан без такого кружка. Микросхема ИП6 (рис. 10) - четыре двунаправленных инвертирующих буферных элемента.

Логика работы входов управления Е1 и Е2

следующая: при лог. 0 на обоих входах передача сигналов происходит от выводов А1 - А4 к выводам В1 - В4, при лог. 1 на обоих входах - от выводов В1 - В4 к А1 - А4. При лог. 1 на входе Е1 и лог. 0 на входе Е2 все информационные выводы микросхемы переходят в Z-состояние, подача лог. 0 на вход Е1 и лог. 1 на вход Е2 одновременно недопустима. Треугольники на графическом обозначении микросхемы и входов Е1 и Е2 символизируют усиление и направление распространения информации при подаче активных сигналов на эти входы. Нагрузочная способность микросхемы ИП6 такая же, как у АПЗ. Микросхема ИП7 отличается от ИП6 только тем, что не инвертирует сигналы. На рис. 12 в качестве примера показано использование буферных микросхем для подключения внешних устройств к компьютеру «Радио-86РК». Если из всех внешних устройств ограничиться лишь таймером КР580ВИ53, его вполне можно смонтировать на плате компьютера без буферных элементов. Если же предполагается подключение нескольких внешних устройств (таймер, часы, АЦПУ, модем и др.), из-за малой нагрузочной способности центрального процессора КР580ВМ80 необходимы буферные элементы. На рис. 12 микросхема DD3 обеспечивает буферизацию управляющих сигналов RD, WR, RES и двух младших адресов АО и А1. Микросхема DD2 буферизирует двунаправленную шину данных. Включение этой микросхемы по входу Е должно происходить лишь при обращении к внешним устройствам, что обеспечивается микросхемой DD1 и элементами D10.4 и D10.3. В основном варианте компьютера «Радио-86РК» адреса А000Н -BFFFH использованы для микросхемы D14. Практически используются только четыре адреса - А000Н, А001Н, А002Н, А00ЗН. Установкой дешифратора DD1 можно обеспечить при сохранении этих адресов для D14 использование следующих четырех адресов А004Н, АООЗН, А006Н, А007Н - для первого внешнего устройства, например таймера; следующих четырех А00ЗН - А00ВН - для второго; следующих четырех А00СН - A00FH - для третьего и т. д., всего можно будет подключить семь дополнительных внешних устройств, для каждого из которых будет отведено четыре адреса.

Если входы 1,2,4 дешифратора DD1 подключить к другим выходам адреса микропроцессора D6, например, А10, All, A12, на каждое внешнее устройство будет отведено по 1024 адреса. Элементы D10.4 и D10.3 необходимы для выключения DD2 при обращении микропроцессора к D14, то есть по адресам А000Н - А00ЗН. В этом случае лог. 0 с выхода О DD1 включает D10.3 и лог. 1 с его выхода выключает DD2. Направление передачи сигнала через DD2 определяется сигналом RD. При чтении из внешнего устройства сигнал RD

принимает значение лог. 0 и происходит передача сигналов через DD2 от внешнего устройства к микропроцессору, в остальных случаях - от микропроцессора к внешнему устройству. На рис. 13 приведены микросхемы -инвертирующие триггеры Шмитта. Микросхема К155ТЛ1 - два четырехвходовых элемента И-НЕ, микросхема ТЛЗ - четыре двухвходовых, микросхема ТЛ2 - шесть инверторов. Указанные микросхемы при плавном изменении входного сигнала обеспечивают скачкообразное переключение выходного (рис. 14). При повышении напряжения на входе элемента микросхемы от нуля выходное напряжение скачком изменяется с лог. 1 на лог. 0 при напряжении на входе около 1,65 В. При снижении напряжения на входе обратное изменение выходного напряжения происходит при напряжении на входе около 0,85 В для триггеров Шмитта серий К155 и К555ТЛ2 и около 1,2 В для КР531ТЛЗ.

Триггеры Шмитта применяют для формирования ТТЛ-сигнала из синусоидального, для приема сигналов при большом уровне помех, в формирователях и генераторах импульсов и в других случаях. На рис. 15, а показана схема формирователя импульса сброса при включении питания, обеспечивающего крутой фронт при большой длительности импульса, на рис. 15, б - простейшего генератора импульсов.

Изучение работы более сложных микросхем удобно продолжить с микросхем последовательностного типа.

Микросхемы комбинационного типа средней степени интеграции

1.4 Микросхемы комбинационного типа средней степени интеграции.

1.4.1 Дешифраторы и шифраторы. 1.4.2 Мультиплексоры. 1.4.3 Преобразователи кодов. 1.4.4 Сумматоры и другие элементы.Микросхемы последовательностного типа

1.3.1 Триггеры. 1.3.2 Счетчики. 1.3.3 Регистры.

Микросхемы последовательностного типа, как уже указывалось, характеризуются наличием памяти. Запись информации в ячейки памяти этих микросхем или изменение содержащейся в них информации производится импульсами. Входы микросхем для подачи импульсов записи могут быть статическими или динамическими. Статические входы характеризуются тем, что импульс, поданный на этот вход, действует в течение всего времени, пока он подан. Как правило, это входы сброса

триггеров, счетчиков и регистров, входы, стробирующие предварительную установку.

Для динамических входов характерно срабатывание по фронту, то есть микросхема чувствительна не к самому импульсу в течение всего времени, пока он подан, а лишь к его фронту или спаду. Точнее, запись (изменение) информации происходит только в моменты смены сигнала на динамическом входе с лог. 1 на лог. 0 или с лог. 0 на лог. 1.

В большинстве случаев для динамических входов безразлично, подаются на вход импульсы положительной или отрицательной полярности (здесь и далее под импульсом отрицательной полярности понимается изменение сигнала с лог. 1 до лог. 0 с последующим изменением с лог. 0 на лог. 1), запись (изменение) информации происходит при изменении сигнала с лог. 1 на лог. 0 для одних типов микросхем, с лог. 0 на лог. 1 для других типов.

При разработке устройств следует придерживаться правила - все последовательностные микросхемы должны переключаться по спадам тактовых импульсов, поэтому при описании микросхем, имеющих динамические входы, указывается, что они срабатывают по спадам импульсов соответствующей полярности. На схемах включения микросхем для импульсов, подаваемых на динамические входы, стрелками отмечены спады импульсов, по которым срабатывают микросхемы, а на графических обозначениях микросхем на их динамических входах штрихом отмечено направление перепада, по которому происходит срабатывание.

Мультиплексоры

Широкое применение в цифровых устройствах находят микросхемы мультиплексоров, используемые для коммутации двоичных сигналов.

Мультиплексор КП7 имеет восемь информационных входов D0 - D7, три адресных входа 1, 2, 4 и вход стробирования S (рис. 105). У микросхемы два выхода - прямой и инверсный. Если на входе стробирования лог. 1, на прямом выходе 0 независимо от сигналов на других входах. Если на входе стробирования лог. 0, сигнал на прямом выходе повторяет сигнал на том входе, номер которого совпадает с десятичным эквивалентом кода на входах 1,2,4 мультиплексора. На инверсном выходе сигнал всегда противофазен сигналу на прямом выходе.

Наличие входа стробирования позволяет простыми средствами строить мультиплексоры на большее число входов. На рис. 106 приведена схема мультиплексора на 16 входов, на рис. 107 - на 64.

Мультиплексор К155КП5 (рис. 105) в отличие от КП7 имеет лишь инверсный выход и не имеет входа стробирования.

Микросхема К155КП1 (рис. 105) содержит четыре адресных входа 1,2,4,8; 16 информационных входов D0 - D15 и вход стробирования S. Выход у этой микросхемы только инверсный. Все свойства и способы включения у нее такие же, как и у КП7.

Микросхема КП2 (рис. 105) содержит два мультиплексора на четыре информационных входа D0 - D3 с отдельными входами стробирования, объединенными адресными входами и прямыми выходами.

Микросхема КП11 (рис. 105) - четыре двухвходовых мультиплексора с общим управлением и возможностью перевода выходов в высокоимпедансное состояние. При лог. 0 на адресном входе А на выход каждого мультиплексора проходит сигнал со входа D0, при лог. 1 -с входа D1. Выходы микросхемы активны при лог. 0 на входе ЕО.

Подача лог 1 на вход ЕО переводит выходы в высокоимпедансное состояние.

Микросхема КП12 (рис. 105) - два четырехвходовых мультиплексора с общим управлением и возможностью перевода выходов в высокоимпедансное состояние. На выход каждого мультиплексора проходит сигнал со входа с номером, соответствующим десятичному эквиваленту двоичного кода, поданного на адресные входы 1 и 2.

Каждый мультиплексор имеет свой вход перевода выхода в высокоимпедансное состояние ЕО, действующий подобно входу ЕО микросхемы К555КП 11. Микросхема КП13 (рис. 105) - четыре двухвходовых мультиплексора с общим управлением и регистром хранения на выходе (похожа на микросхему КР531ИР20). На входы регистра поступают сигналы

со входов D0 микросхемы, если на адресном входе А лог. 0 и со входов D1, если на входе А лог. 1. Запись в регистр производится по спаду импульса положительной полярности на входе С. Микросхема КП14 (рис. 105) аналогична микросхеме К555КП11, но инвертирует мультиплексируемые сигналы. Микросхема КП15 (рис. 105) - восьмивходовый мультиплексор с прямым и инверсным выходом и с возможностью перевода выходов в высокоимпедансное состояние. При лог. 0 на входе ЕО на выходы проходит сигнал с того входа, номер которого соответствует десятичному эквиваленту кода, поданного на адресные входы 1, 2, 4. На инверсный выход сигнал проходит с инверсией. Подача лог. 1 на вход ЕО переводит и прямой, и инверсный выходы в высокоимпедансное состояние. Микросхема КП16 (рис. 105) - четыре двухвходовых стробируемых мультиплексора. Логика ее работы аналогична логике работы микросхемы КП11, однако подача лог. 1 на вход S переводит выходы микросхемы в состояние лог. 0 независимо от состояния информационных и адресного входов. Микросхема КР533КП17 (рис. 105) аналогична микросхеме КП12, но инвертирует мультиплексируемые сигналы. Микросхема КП18 (рис. 105) аналогична КП16, но инвертирует мультиплексируемые сигналы. Подача лог. 1 на вход S микросхемы устанавливает выход в состояние лог. 1 независимо от состояния других входов. Микросхема КР1533КП19 (рис. 105) функционирует аналогично КП2, но инвертирует мультиплексируемые сигналы. Вход S этой микросхемы действует аналогично такому же входу КП18. Наиболее полный набор мультиплексоров входит в серию микросхем КР1533 - счетверенные мультиплексоры на два входа, сдвоенные на четыре входа и мультиплексоры на восемь входов, причем в каждой из этих групп есть мультиплексоры со стандартным выходом - КР1533КП16, КР1533КП2, КР1533КП17, с инверсным выходом - КР1533КП18, КР1533КП19, КР1533КП7, с выходом с высокоимпедансным состоянием - КР1533КП11, КР1533КП12, КР1533КП15, с инверсным выходом с высокоимпедансным состоянием - КР1533 КП14, КР1533КП17, КР1533КП15. Нагрузочная способность мультиплексоров КР1533КП2, КП7, КП11А, КП12, КП14А, КП15 составляет 12 мА в состоянии лог. 0 при выходном напряжении 0,4 В и 0,4 мА в состоянии лог. 1 при вы

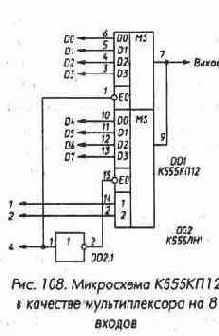

ходном напряжении 2, 4 В, мультиплексоров КР1533КП16, КП17, КП18, КП19 аналогична той, что у микросхемы КР1533ИР22. Нагрузочная способность мультиплексоров серии КР531, выходы которых могут переводиться в высокоимпедансное состояние, составляет 20 мА в состоянии лог. 0 и 6,5 мА в состоянии лог. 1 при выходном напряжении 2,4 В. Возможность перевода выходов мультиплексоров КП11, КП12, КП14, КП15 и КП17 в высокоимпедансное состояние облегчает объединение микросхем для увеличения числа входов. На рис. 108 показано преобразование мультиплексоров

микросхемы КП12 в один на восемь входов, на рис. 109 - на 64 входа. Назначение выводов микросхем КП12 и К155КП2, КП15 и К155КП7 совпадает за исключением входов перевода выходов микросхем в высокоимпедансное состояние. Это позволяет в большинстве случаев использовать микросхемы КП12 и КП15 взамен указанных микросхем серии К155 без переработки печатных плат.

Общие сведения

У нас в стране обширна номенклатура выпускаемых интегральных микросхем. Для построения устройств автоматики и вычислительной техники широкое применение находят цифровые микросхемы серии К 155, которые изготавливают по стандартной технологии биполярных микросхем транзисторно-транзисторной логики (ТТЛ). Имеется свыше 100 наименований микросхем серии К 155. При всех своих преимуществах - высоком быстродействии, обширной номенклатуре, хорошей помехоустойчивости - эти микросхемы обладают большой потребляемой мощностью. Поэтому им на смену выпускают микросхемы серии К555, принципиальное отличие которых - использование транзисторов с коллекторными переходами, зашунтированными диодами Шоттки. В результате транзисторы микросхем серии К555 не входят в насыщение, что существенно уменьшает задержку выключения транзисторов. К тому же они значительно меньших размеров, что уменьшает емкости их р-n-переходов. В результате при сохранении быстродействия микросхем серии К555 на уровне серии К155 удалось уменьшить ее потребляемую мощность примерно в 4...5 раз.

Дальнейшее развитие микросхем серий ТТЛ - разработка микросхем серии КР1533. Основное эксплуатационное отличие их от схем серии К555 - в 1.5...2 раза меньше потребляемая мощность при сохранении и повышении быстродействия.

Средняя задержка распространения элементов микросхем серии К155, К555, КР1533 примерно 15...20 нс. В случаях, когда требуется более высокое быстродействие, используют микросхемы серии КР531. Для сравнения основных параметров в табл. 1 приведены значения средней потребляемой мощности Рср и средней задержки tз.ср распространения микросхем ТТЛ указанных серий, а также стандартные значения входных Iвх и выходных Iвых токов и нагрузочной способности N указанных серий микросхем. Некоторые микросхемы допускают большие выходные токи и имеют большую нагрузочную способность, чем указано в табл. 1. Часть микросхем (особенно серии КР531) также имеют отличные от стандартных входные токи. Эти отличия специально указаны далее.

Стандартные выходные уровни лог. 1 составляют 2,4...2,7 В, лог. 0 -0,36...0,5 В.

Напряжение питания микросхем серий ТТЛ 5 В +-5%, для серии КР1533 допуск на напряжение питания +-;10%.

Микросхемы выпускают в пластмассовых корпусах с 8, 14, 16, 20, 24, 28 выводами, температурный диапазон их работоспособности:

-10...+70 °С. Часть микросхем серий К155 и К555 выпускают в керамических корпусах (их обозначение КМ155 и КМ555), температурный диапазон работоспособности таких микросхем -45...+85 °С. На рис. 1 приведены зависимости выходного напряжения от входного для инвертирующих логических элементов упомянутых серий микросхем при температуре +20 С. Поскольку за порог переключения принимается входное напряжение, при котором выходное равно ему, его нетрудно найти по приведенным зависимостям как точку пересечения с прямой Uвых = Uвх. Из рисунка видно, что микросхемы серии КР1533 имеют наибольший порог переключения - 1,52 В и, как следствие, наибольшую помехоустойчивость. Рассматриваемые серии имеют в своем составе однотипные микросхемы с совпадающими после номера серии цифробуквенными обозначениями. Логика работы однотипных микросхем, за редким ис-

ключением, отмеченным далее, совпадает. Микросхемы серии КР531 ранее не имели в обозначении буквы «Р», а имели в конце обозначения букву <<П>>, например К531ЛАЗП. В табл. 2 приведены обозначение большинства рассматриваемых микросхем, функциональное назначение, число выводов корпуса, средняя потребляемая мощность, средняя задержка распространения сигнала и номер рисунка, на котором приведено графическое обозначение микросхемы. В функциональном назначении буквы означают: OK - микросхемы имеют выход с открытым коллектором, ОЭ - с открытым эмиттером, Z - выходы могут переводиться в высокоимпедансное состояние. При разработке принципиальных схем различных устройств всегда возникает вопрос: что делать с- неиспользуемыми входами интегральных микросхем. Если по логике работы на вход необходимо подать лог. 0, то его соединяют с общим проводом, если лог. 1 - возможны варианты. Во-первых, неиспользуемые входы микросхем серии К155 можно никуда не подключать, то есть подпаивать к контактной площадке минимальных размеров, к которой (это важно) не подключены никакие проводники. Но при этом несколько уменьшается быстродействие микросхем.

Для микросхем серий К555, КР531, КР1533 оставлять входы неподключенными не допускается. Во-вторых, возможно подключение неиспользуемых входов к используемым входам того же элемента, но это увеличивает нагрузку на микросхему-источник сигнала, что также снижает быстродействие. В-третьих, можно подключать неиспользуемые входы микросхем серий К155 и КР531 к выходу инвертирующего элемента, входы которого при этом надо соединить с общим проводом. Наконец, можно объединять неиспользуемые входы микросхем этих серий и подключать их к источнику питания +5 В через резистор сопротивлением 1 кОм (до 20 входов к одному резистору). Входы микросхем серий К555 и КР1533 можно подключать к источнику питания +5 В непосредственно. Недопустимо подключать ко входу микросхемы проводник, который во время работы может оказаться неподключенным к выходу источника сигнала, например при управлении от кнопки или переключателя, так как это резко снижает помехоустойчивость устройства. Такие проводники следует подключать к источнику +5 В через резистор сопротивлением 1 кОм (до 20 входов к одному резистору). Входы микросхем серий К555 и КР1533 можно подключать к источнику питания +5 В непосредственно. На печатных платах с использованием микросхем серий К155, К555, КР1533 необходима установка блокировочных конденсаторов между цепью +5 В и общим проводом. Их число определяется одним-двумя конденсаторами емкостью 0,033...0,15 мкВ на каждые пять микросхем. Конденсаторы следует располагать на плате по возможности равномерно. Их следует также установить рядом со всеми микросхемами с мощным выходом (например, К155ЛА6) или с потребляемой мощностью более 0,5 Вт. Микросхемы серий КР531 требуют особого внимания при разводке цепей питания и общего провода. При изготовлении промышленных

устройств на микросхемах этой серии используют многослойные печатные платы, один из слоев используют в качестве общего провода, другой - в качестве шины питания. Если используют двухслойные платы, шины питания и общего провода выполняют навесными в виде латунных полос шириной около 5 мм, керамические блокировочные конденсаторы емкостью 0,047...0,15 мкФ подпаивают непосредственно к этим шинам (один конденсатор на одну-две микросхемы).

В радиолюбительских условиях можно одну сторону печатной платы использовать под общий провод, другую - под сигнальные цепи и под провод питания, конечно, при этом придется устанавливать много перемычек и к каждой микросхеме блокировочный конденсатор. Как правило, напряжение питания микросхем подводят к выводу с максимальным номером, общий провод - к выводу, номер которого вдвое меньше. Случаи исключения из этого правила приведены в табл. 3. Микросхемы серий К555 и КР1533 можно применять вместо однотипных микросхем серии К 155 и совместно с ними, при этом следует иметь в виду, что их нагрузочная способность на микросхемы серии К155 составляет 5. Микросхемы серии КР531 следует применять только в случае необходимости высокого быстродействия, так как они создают большой уровень помех, к которым особенно чувствительны микросхемы серии К555, и потребляют большую мощность. Цифровые микросхемы по своим функциям делятся на два больших класса - комбинационные и последовательностные. К первому

относятся микросхемы, не имеющие внутренней памяти (состояние выходов этих микросхем однозначно определяется уровнями входных сигналов в данный момент времени). Ко второму - микросхемы, состояние выходов которых определяется не только уровнями входных сигналов в данный момент времени, но и последовательностью состояний в предыдущие моменты времени из-за наличия внутренней памяти. К комбинационным относятся простые логические микросхемы И-НЕ, И-ИЛИ-НЕ, НЕ, ИЛИ-НЕ, И, ИЛИ, более сложные элементы - дешифраторы, мультиплексоры, сумматоры по модулю 2, полные сумматоры, преобразователи кодов для семисегментных и матричных индикаторов, шифраторы, программируемые постоянные запоминающие устройства, преобразователи двоично-десятичного кода в двоичный и обратно, однонаправленные и двунаправленные буферные элементы, мажоритарные клапаны, триггеры Шмитта, которые, однако, имеют внутреннюю память и могут быть отнесены и к последовательностным микросхемам, а также некоторые другие. К последовательностным микросхемам относятся триггеры, счетчики, сдвигающие регистры, оперативные запоминающие устройства и некоторые другие микросхемы. Ждущие мультивибраторы нельзя отнести однозначно ни к одному из упомянутых классов, так как внутренняя память этих микросхем помнит изменение входных сигналов ограниченное время, после чего состояние выходов микросхемы ни от чего не зависит.То же самое относится и к генераторным микросхемам.

Преобразователи кодов

Для формирования цифр и знаков на семисегментных и матричных индикаторах и запуска шкальных индикаторов используют различные преобразователи кодов, иногда неправильно называемые дешифраторами. Существуют также микросхемы для преобразования двоичного кода в двоично-десятичный, и наоборот. Рассмотрим такие микросхемы.

Микросхема К155ПП5 - преобразователь двоично-десятичного кода в код семисегментного индикатора (рис. 110), ее можно применять совместно с полупроводниковыми индикаторами с общим анодом, например АЛ305А или АЛС324Б. Для нормирования тока элементов индикатора между его катодами и выходами микросхемы следует включить ограничительные резисторы, сопротивление которых определяется в соответ

ствии с рабочим током индикатора. Вход Е микросхемы может быть использован для гашения индикатора, которое происходит при подаче на этот вход лог. 1. Индикация осуществляется при лог. 0.

На рис. 111 приведено стандартное обозначение сегментов семисегментных индикаторов, а на рис. 112 - форма индицируемых знаков.

Микросхемы КМ155ИД8А, КМ155ИД8Б, КМ155ИД9 - преобразователи двоично-десятичного кода 1-2-4-8 в коды работы индикаторов, состоящих из 27 отдельных светодиодов (ИД8, рис. 113) и из 20 светодиодов (ИД9, рис. 114). Микросхемы имеют по четыре входа для подачи

входного кода. Число выходов микросхемы КМ155ИД8 составляет 18, микросхемы КМ155ИД9 - 13.

К каждому выходу микросхем должны быть подключены или один, или два последовательно включенных светодиода, соединенных с источником питания +5 В. На рис. 113 (б) и 114 (б) на элементах индикаторов указаны номера выводов микросхем, к которым должны быть подключены светодиоды индикаторов. Микросхемы выполнены с «открытым» коллекторным выходом и содержат ограничительные резисторы двух номиналов - для выходов, стыкуемых с двумя последовательно включенными светодиодами, номинал ограничительного резистора меньше, что обеспечивает одинаковый ток

через все светодиоды индикатора - 10 мА для микросхем КМ155ИД8А и КМ155ИД9 и 15 мА для КМ155ИД8Б.

Для входных кодов чисел 0-9 на светодиодах индицируются соответствующие цифры, для кода числа 10 знак «-», для кода числа 11 - буква «Е».

Для кодов чисел 12- 15 все светодиоды индикаторов погашены.

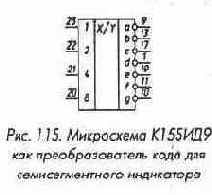

Микросхема КМ155ИД9 может быть использована и с обычными полупроводниковыми семисегментными индикаторами с общим анодом аналогично К155ПП5 (рис. 115). В отличие от использования микросхемы К155ПП5 не требуются ограничительные резисторы и добавляется возможность индикации знака «-» и буквы «Е». При необходимости можно увеличить число диодов в индикаторах, управляемых от микросхемы КМ155ИД9, до 27 (рис. 116, а) и до 34 (рис. 116, б). В этом случае напряжение питания цепочек из трех светодиодов должно быть увеличено до 7 В, а для четырех светодиодов - до 9 В. Одиночные светодиоды должны быть по-прежнему подключены к источнику питания +5 В. ; Микросхема КМ155ИД11 - преобразователь двоичного кода в код управления светодиодной шкалой, формирующий светящийся «столбик», число светящихся точек в котором равно числу, соответствующему входному коду (рис. 117). Микросхема имеет три входа 1, 2, 4 для подачи входного кода, вход разрешения Е, вход переноса PI, восемь выходов для подключения светодиодной шкалы 0-7 и выход переноса Р.

При подаче лог. 1 на вход PI и лог. 0 на вход Е лог. 1 появляется на том выходе микросхемы, номер которого соответствует десятичному эквиваленту кода на входах 1, 2, 4 и на всех выходах с меньшим номером, при этом на выходе Р -лог. 0. Если на вход PI подать лог. 0, на выходах 0-7 будет лог. 1, на выходе Р -лог. 0 независимо от сигналов на входах Е и 1,2,4. Если на входах PI и Е лог. 1, на выходах 0-7 лог. 0, на выходе Р - лог. 1. Выходы микросхем выполнены с от-

крытым эмиттером и ограничительным резистором, обеспечивающим выходной ток для непосредственного подключения светодиодов между выходами и общим проводом. При работе одной микросхемы с восемью светодиодами высота «столбика» светящихся светодиодов будет на единицу больше десятичного эквивалента кода на входах 1,2,4. Рис. 118 иллюстрирует соединение двух микросхем КМ155ИД11 для индикации 16 уровней. Если на входе 8 устройства по схеме рис. 118 лог. 0, на выходе Р DD1 лог. 1, микросхема DD2 работает так, как описано выше, и светодиоды HL1 - HL8 образуют столбик, высота которого на единицу больше численного эквивалента кода на входах 1,2,4.

Если на входе 8 устройства лог. 1, на входе разрешения Е микросхемы DD1 появится лог. 0, в работу вступит DD1 и в соответствии с поданным на входы 1,2,4 кодом начнут включаться светодиоды HL9 - HL16. На выходе Р появится лог. 0, он подается на вход PI DD2 и включит все светодиоды HL1 - HL8 независимо от сигналов на других входах DD2.

Таким образом, в схеме рис. 118 число светящихся диодов на единицу больше десятичного эквивалента входного кода - входному коду 0000 соответствует один включенный светодиод HL1, коду 1111-16 светодиодов. Для построения шкал с большим числом индицируемых уровней необходим дополнительный дешифратор, например К155ИД4 (рис. 119). Работает такое устройство аналогично. Если на входах 8 и 16 лог. 0, то лог. 0 с выхода 0 DD1 включает DD5, высота столбика составляет 1-8 светодиодов. Если на входе 8 лог. 1, на входе 16 - лог. 0, включается DD4, лог. 0 с ее выхода Р включает HL1 - HL8. При лог. 1 на входах 8 и 16 начинает работать DD2, лог. 0 с ее выхода Р включает HL17 -HL24, на выходе Р DD3 появляется лог. 0, включающий HL9 - HL16, лог. 0 с выхода Р DD4 включает HL1 - HL8. Таким образом, и здесь число светящихся светодиодов на единицу больше десятичного эквивалента входного кода. Вход Е устройства по схеме рис. 119 можно использовать для гашения шкалы - при подаче на него лог. 1 все светодиоды будут выключены независимо от сигналов на входах 1-16. При необходимости построения шкал с большим числом индицируемых уровней необходимо использовать соответствующее число микросхем К155ИД11 и дешифратор с большим числом выходов (К155ИД4 в соответствующем включении, К555ИД7, К155ИДЗ). Микросхема КМ155ИД12 - стробируемый дешифратор трехразрядного двоичного кода, подаваемого на входы 1-2-4, в позиционный (рис. 117). Лог. 1 появляется на том выходе микросхемы, номер которого соответствует десятичному эквиваленту входного кода, при этом на входе Е должен быть лог. 0. Если на вход Е подать лог. 1, на всех выходах будет лог. 0. К выходам этой микросхемы можно подключить светодиоды шкалы аналогично КМ155ИД11, в результате в шкале будет светиться один светодиод с номером, на единицу большим десятичного эквивалента входного кода. При необходимости можно соединять микросхемы КМ155ИД12 в соответствии с рис. 118 или 119, естественно, исключив цепи выводов Р и PI.

Микросхема КМ155ИД13 имеет те же выводы, что и КМ155ИД11, но иную логику работы. Она обеспечивает построение шкал, в которых светятся одновременно два рядом расположенных светодиода -один с номером, на единицу большим десятичного эквивалента входного кода, и второй с номером, равным эквиваленту. При подаче на вход PI лог. 1, на вход Е лог. 0 входному коду 000 соответствует лог. 1 на выходе 0, входному коду 001 - лог. 1 на выходах 0 и 1, коду 010 - лог. 1 на выходах 1 и 2 и т. д. Кроме того, входному коду 000 и лог.0 на входе Е соответствует лог. 0 на выходе Р (во всех остальных случаях на выходе Р лог. 1). Лог. 0 на входе PI включает светодиод, подключенный к выходу 7, независимо от всех других входных сигналов, этот вход не влияет ни на какие другие выходы. При соединении микросхемы КМ155ИД13 по схемам рис. 118 или 119 можно получить устройства, в которых положение двух светящихся светодиодов будет определяться входным сигналом так же, как это описано для одной микросхемы КМ155ИД13 - номер верхнего светодиода на единицу больше десятичного эквивалента входного кода, ниже его светится еще один светодиод. Нулевому входному коду соответствует свечение одного светодиода HL1. Микросхема К555ИД18 (рис. 120) - преобразователь двоично-десятичного кода 1-2-4-8 в сигналы управления семисегментным индикато-

ром, имеет выходы с открытым коллектором и предназначена для управления полупроводниковыми индикаторами с общим анодом, которые подключаются к выходам микросхемы через ограничительные резисторы (рис. 121). Особенность микросхемы - возможность гашения левых незначащих нулей при индикации многоразрядных чисел и возможность одновременного включения всех сегментов индикатора для контроля его исправности. Для обеспечения указанных режимов используют два входа - Е0 и К и двунаправленный вывод Е. Обычный режим преобразования входного кода осуществляется при подаче на входы Е0 и К лог. 1, вывод Е можно при этом оставить свободным - в состав микросхемы входит резистор (сопротивлением около 5 кОм), включенный между выводом Е и цепью +5 В. Если на вывод Е подать лог. 0, независимо от состояния всех остальных входов происходит гашение всех сегментов индикатора, подключенного к выходам микросхемы.

Если на вывод Е подать лог. 1 или оставить его свободным, а на вход К (Контроль) подать лог. 0, независимо от сигналов на других входах включаются все сегменты индикатора. Наиболее интересный режим осуществляется в следующем случае: на входе К лог. 1, вывод Е свободен, на входе Е0 (гашение нуля) лог. 0. В этом случае при подаче на выходы 1,2,4,8 входного кода, соответствующего цифрам 1-9, происходит индикация этих цифр, при подаче кода цифры 0 - гашение индикатора и выдача на вывод Е лог. 0. Поэтому, если соединить несколько микросхем К555ИД18 и индикаторов в соответствии с рис. 121, можно получить гашение всех незначащих нулей в старших разрядах. Если в старшем разряде (DD1) должен индицироваться нуль, он гасится и на выводе Е DD1 появляется лог. 0, разрешающий гашение нуля в DD2, и т. д. Если во всех разрядах нуль, то ни один из индикаторов не включен, на выводе Е микросхемы младшего разряда - лог. 0, являющийся признаком подачи нулевого числа, этот сигнал может быть использован, например, в таймерах. Если необходимо, чтобы при всех нулях младший разряд не гасился, на вход Е0 младшего разряда нужно подать лог. 1. Если нужно обеспечить контроль индикаторов в схеме рис. 121, на объединенные входы К всех микросхем можно подать лог. 0. Для

принудительного гашения всех индикаторов на рис. 121 независимо от входного кода на выводы Е всех микросхем можно подать лог. 0 от соответствующего числа элементов с открытым коллектором, например К555ЛН2. Сочетание включенных сегментов при входных кодах, соответствующих числам 10-14, не соответствует никаким буквам или знакам, при входном коде 15 происходит гашение индикатора. Для микросхемы К555ИД 18 максимальное напряжение, подводимое к выходам, находящимся в состоянии лог. 1,15 В, максимальный выходной ток в состоянии лог. 0-24 мА.

Для генерации знаков на 35-элементных индикаторах и дисплеях можно использовать микросхемы К155РЕ21, К155РЕ22, К155РЕ23, К155РЕ24: К155РЕ21 - для воспроизведения русских букв (за исключением «Ъ»), К155РЕ22 -букв латинского алфавита, буквы <<Ъ>> и некоторых знаков, К155РЕ23 - цифр и различных знаков (табл. 5).

Каждая из этих микросхем содержит основную часть необходимой информации, недостающая часть содержится в микросхеме К155РЕ24. Цоколевка всех четырех микросхем одинакова (рис. 122), в микросхеме К155РЕ24 вывод 9 не используется. Каждая микросхема со держит три входа выбора строки в матричном индикаторе В1, В2, В4, пять входов выбора индицируемого знака А1 - А16, два входа разрешения Е. Входы Е разрешают появление сигналов лог. 0 на выходах микросхемы лишь при подаче лог. 0 на оба входа Е. При подаче на входы В1, В2, В4 кода номера строки на выходах 1,2, 3,4 микросхемы появляется лог. 0 для включения элементов индикатора данной строки. Крайнему левому элементу строки соответствует сигнал на выходе 1, второму слева - на выходе 2 и т. д. Для крайнего правого элемента должна использоваться информация с одного из трех выходов микросхемы К155РЕ24. Выход 3 этой микросхемы дополняет информацию микросхемы К155РЕ21, выход 2 - микросхемы К155РЕ22, выход 1 - микросхемы К155РЕ23. Счет строк индикатора ведется сверху вниз: первой строке соответствует код 001 (младший разряд - В1), последней - код 111. Код 000 не используется. Индицируемый знак определяется кодом, подаваемым на входы выбора знака А1 - А16 в соответствии с табл. 5. На рис. 123 приведена схема соединения микросхем К155РЕ21, К155РЕ22, К155РЕ23, К155РЕ24 между собой, обеспечивающая получение информации, необходимой для индикации всех указанных в табл. 5 знаков. Выходы микросхем выполнены с открытым коллектором, что позволяет объединить их между собой и требует установки нагрузочных резисторов R1 - R7. Старшие разряды кода индицируемого знака А32 и А64 выбирают микросхему (DD1, DD2 или DD3), Таблица 5

| N | Адрес | Индицируемый знак для микросхем | ||||||

| А16 | А8 | А4 | А2 | А1 | К155РЕ21 | К155РЕ22 | К155РЕ23 | |

| А32=1 А64=0 | А32=0 А64=1 | А32=1 А64=1 | ||||||

| 0 1 2 3 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 1 1 | 0 1 0 1 | Ю А Б Ц | @ А В С | пробел ! кавычки # |

| 4 5 6 7 | 0 0 0 0 | 0 0 0 0 | 1 1 1 1 | 0 0 1 1 | 0 1 0 1 | Д Е Ф Г | D E F G | * % & апостроф |

| 8 9 10 11 | 0 0 0 0 | 1 1 1 1 | 0 0 0 0 | 0 0 1 1 | 0 1 0 1 | Х И Й К | Н I J K | ( ) * + |

| 12 13 14 15 | 0 0 0 0 | 1 1 1 1 | 1 1 1 1 | 0 0 1 1 | 0 1 0 1 | л м н о | L М N 0 | , - . / |

| 16 17 18 19 | 1 1 1 1 | 0 0 0' 0 | 0 0 0 0 | 0 0 1 1 | 0 1 0 1 | п я Р с | Р Q R S | 0 1 2 3 |

| 20 21 22 23 | 1 1 1 1 | 0 0 0 0 | 1 1 1 1 | 0 0 1 1 | 0 1 0 1 | т у ж в | Т U V W | 4 5 6 7 |

| 24 25 26 27 | 1 1 1 1 | 1 1 1 1 | 0 0 0 0 | 0 0 1 1 | 0 1 0 1 | ь ы 3 ш | Х Y Z [ | 8 9 : ; |

| 28 29 30 31 | 1 1 1 1 | 1 1 1 1 | 1 1 1 1 | 0 0 1 1 | 0 1 0 1 | э щ ч пробел | \ ] ^ ъ | < = > ? |

а также необходимый выход микросхемы DD4 с помощью мультиплексора DD6. При А32 - А64 - 0 ни одна из микросхем DD1 - DD3 не выбрана, на выходах 1-5 лог. 1. Если на входе А32 лог. 1, на входе А64 - лог. 0, включается DD1, на выход 5 проходит информация с выхода 3 микросхемы DD4, индицируются русские буквы. При лог. 0 на входе А32 и лог. 1 на входе А64 выбирается микросхема DD2, индуцируются буквы латинского алфавита, при А32=А64=1 индицируются цифры и знаки. Вполне возможны другие варианты подключения входов Е микросхем к старшим разрядам источника кода знаков. Если какая-либо из микросхем оказывается лишней, например, не используются латинские буквы, вместо мультиплексора DD6 можно использовать микросхему К155ЛАЗ (рис. 124). В этом случае при А32 = 0 выбирается DD1 и индицируются русские буквы, при А32 = 1 выбирается DD3, происходит индикация цифр и знаков.

Как пример использования микросхем К155РЕ21 - К155РЕ 24, рассмотрим схему индикатора для четырех знаков с использованием светодиодных матриц АЛС340А (рис. 125). На этой схеме DD4 обозначены элементы схемы рис. 123 (резисторы R1 - R4 в этом случае на рис. 123 не нужны). Генератор DD1.1, DD1.2, DD1.3 со счетчиком строк DD2, DD3 обеспечивает на выходах последних поочередное появление кодов 00000, 00001, 00010...11111 и снова 00000 и т. д. Подключенные к выходам DD2 и DD3 дешифраторы DD5 и DD6 поочередно включают транзисторы VT6 - VT33. В результате поочередно на строки индикаторов HL1 - HL4 подается напряжение около +0,8 В. К выводам строк индикаторов подключены катоды светодиодов, расположенных на пересечении строк и столбцов. Аноды светодиодов подключены к выводам столбцов. Напряжение +5 В подается на выводы столбцов через ключи на транзисторах VT1 -VT5, управление ключами ведется от выходов 1-5 DD4. Ток через диоды индикаторов ограничен резисторами R12 - R16 на уровне около 100 мА. Скважность импульсов тока - 32, средний ток через каждый светящийся светодиод - около 3 мА, что обеспечивает нормальную яркость его свечения. Перебор строк одного индикатора идет сверху вниз, перебор индикаторов - слева направо.

Состояниям счетчика строк 00000, 010000, 10000,11000 не соответствует выбор каких-либо строк индикаторов,

выходы 0 и 8 дешифраторов DD5 и DD6, соответствующие этим состояниям, не использованы. Индицируемые знаки определяются кодами, подаваемыми на входы А1 - А64 DD4. Смена этих кодов должна осуществляться в моменты перехода от одного индикатора к другому. Для смены кодов можно использовать мультиплексоры, например К155КП2, управляемые с выходов 1 и 2 устройства. Лог. 0 на обоих выходах 1 и 2 соответствует включению индикатора HL1, лог. 1 на выходе 1 и лог. 0 на выходе 2 - индикатора HL2 и т. д. Десятичная точка перед индицируемыми цифрами может быть включена переключателем SA1. Транзисторы КТ626А можно заменить на КТ626 с любым буквенным индексом или на транзисторные матрицы КТС622А, Б. Если необходимо вывести большое число знаков, возможно пропорциональное наращивание числа выходов дешифратора счетчика строк (при одновременном увеличении числа разрядов счетчика), однако возможен более экономичный вариант, например, на рис. 126 приведена измененная часть схемы рис. 125 для индикации восьми знаков. В этой схеме, так же как и в схеме рис. 125, используется дешифратор на 28 выходов, однако индикаторы объединены в две группы. Первая группа индикаторов по столбцам управляется транзисторами VT1 -VT5, вторая - транзисторами VT34 - VT38. Пока на выходе 2 микросхемы DD3 счетчика строк (он должен быть в этом случае шестиразрядным)

лог. 0, выходные сигналы через микросхемы DD7 и элемент DD9.1 включают транзисторы VT1 - VT5 и поочередно включаются индикаторы HL1 - HL4. Когда на выходе 2 микросхемы DD3 появляется лог. 1, выходные сигналы ПЗУ проходят через микросхему DD8 и элемент DD9.2 на транзисторы VT34 - VT38, включаются индикаторы HL5 - HL8. Скважность импульсов тока через светодиоды в схеме рис. 126 составляет 64, поэтому амплитуда импульсов увеличена до 200 мА за счет уменьшения сопротивления токоограничительных резисторов. Рассмотренный вариант включения индикаторов (рис. 126) может быть использован и при меньшем, чем восемь, числе разрядов.

Описанные выше микросхемы К155РЕ21 - К155РЕ24 являются постоянными запоминающими устройствами (ПЗУ), запись информации в которые произведена на заводе. В состав серии К155 входит микросхема ПЗУ К155РЕЗ (рис. 127), программирование которой для изготовления необходимого преобразователя кодов может быть произведено потребителем. Микросхема К155РЕЗ имеет пять адресных входов 1, 2, 4, 8, 16, вход раз решения Е, восемь выходов. Микросхема позволяет записать 32 восьмиразрядных двоичных слова и может быть широко использована при разработке различных радиоэлектронных устройств. При изготовлении микросхемы на заводе во все слова по всем адресам записывают лог. 0. При программировании потребитель может записать в определенные биты слов лог. 1 и получить ПЗУ с нужной информацией. Микросхема К155РЕЗ имеет «открытые» коллекторные выходы, что позволяет объединять микросхемы по выходам, управление выбором нужной микросхемы осуществляется подачей лог. 0 на вход Е микросхемы. Для микросхем, на входы Е которых подана лог. 1, на всех выходах также лог. 1. До программирования все входы микросхемы равноценны, как равноценны и ее выходы, что позволяет использовать их в произвольном порядке, чем упрощается разводка печатных плат. Предприятие-изготовитель не гарантирует полную программируемость микросхем К155РЕЗ (примерно в половину новых микросхем необходимую информацию записать нельзя). Примером использования микросхем К155РЕЗ является изготовление преобразователей кода для индикации цифр и некоторых букв на семи- и девятисегментных индикаторах.

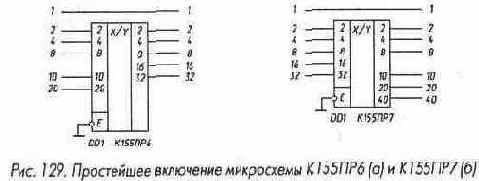

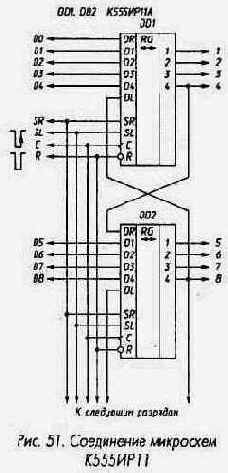

Микросхемы К155ПР6 и К155ПР7 (рис. 128) служат для преобразования двоично-десятичного кода в двоичный (К155ПР6) и двоичного кода в двоично-десятичный (К155ПР7). Микросхемы являются постоянными запоминающими устройствами, программирование которых произведено на заводе-изготовителе. По функциональному назначению выво дов указанные микросхемы идентичны микросхемам К155РЕЗ. Включение микросхем К155ПР6 и К155ПР7 в простейшем варианте проиллюстрировано на рис. 129.

Одна микросхема К155ПР6 позволяет преобразовать двоично-десятичный код чисел 0-39 в двоичный. Младший разряд (разряд единиц) передается мимо микросхем, так как он совпадает в двоично-десятичном и двоичном кодах. Аналогично одну микросхему К155ПР7 можно использовать для преобразования двоичного кода чисел 0-63 в двоично-десятичный.

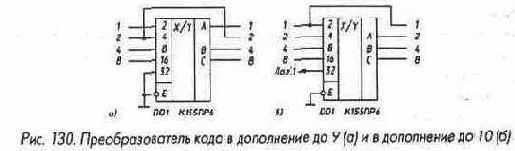

Микросхема К155ПР6 позволяет также преобразовать двоично-десятичный код чисел 0-9 в код дополнения до 9 (рис. 130, а) и до 10 (рис. 130, б). Сумма десятичных чисел, соответствующих входному и выходному кодам схемы рис. 130 (а), равна 9, а схемы рис. 130 (б) - 10. В схеме рис. 130 (б) при входном коде, соответствующем числу 0, выходной код также соответствует 0.

Микросхему К155ПР6 можно применять для преобразования данных, вводимых в двоично-десятичном коде, в двоичный, например для управления микросхемой К155ИЕ8 в синтезаторе частоты или для ввода двоично-десятичного кода в цифроаналоговый преобразователь, работающий, как правило, в двоичном коде. Микросхема К155ПР7 может быть использована для преобразования в десятичный вид данных, полученных в двоичном коде, например с выхода аналогоцифрового преобразователя для индикации в десятичном виде.

Как правило, разрядности одиночных микросхем недостаточно для решения большинства задач преобразования кодов, в этих случаях применяют каскадное соединение микросхем. На рис. 131 показано соединение двух микросхем К155ПР6 для преобразования двоично-десятичных кодов чисел 0-99 в двоичный, на рис. 132 -шести микросхем для преобразования кодов чисел 0-999. На рис. 133 и 134 представлены схемы для преобразования двоичных

кодов чисел 0-255 и 0-511 в десятичный. Отметим, что для преобразования кодов десятичных чисел 0-9999 в двоичный требуется 19 микросхем К155ПР6, а для преобразования кодов двоичных чисел 0-4095 и 0-65535 в двоично-десятичный - соответственно 8 и 16 микросхем К155ПР7. Микросхемы К155ПР6 и К155ПР7 выполнены с «открытым» коллекторным выходом, поэтому для обеспечения помехоустойчивой работы микросхем между их выходами и плюсом питания следует устанавливать нагрузочные резисторы 1...5.1 кОм, эти резисторы на приведенных схемах условно не показаны.Вход разрешения работы микросхем Е должен быть подключен к общему проводу, при подаче на него лог. 1 все выходы переходят в выключенное состояние.

Регистры

Регистры можно разделить на два класса - сдвигающие и хранения информации. В свою очередь, регистры хранения бывают «прозрачные», тактируемые импульсом, и синхронные, тактируемые фронтом импульса.

Микросхемы К155ТМ5 и ТМ7 (рис. 48) содержат по четыре триггера, образующих два двухразрядных регистра хранения информации. Каждый триггер имеет информационный вход D, тактовый вход С и прямой выход (а в микросхеме ТМ7 еще и инверсный выход). Триггер работает следующим образом. При лог. 0 на входе С изменение сигнала на входе D не влияет на состояние триггера и он хранит записанную в нем ранее информацию. При подаче на вход С лог. 1 триггер превращается в повторитель - сигнал на выходе соответствует сигналу на входе, за это свойство подобные триггеры называют «прозрачными». При подаче на вход С лог. 0 триггер переходит вновь в режим хранения, а его состояние определяется сигналом на входе D перед спа-

дом импульса на входе С. Таким образом, основные свойства триггеров микросхем К155ТМ5 и ТМ7 следующие:

1) при подаче на вход С лог. 0 - хранение информации;

2) при подаче на вход С лог. 1 - повторение входного сигнала;

3) запоминается информация, имеющаяся на входе D перед спадом на входе С;

4) изменение информации на выходе может происходить в течение всего положительного импульса на входе С, если при этом меняется информация на входе D.

Эту разновидность D-триггера называют «D-триггером, тактируемым импульсом», «триггером-защелкой», «прозрачным» триггером, чтобы отличать ее от описанных выше D-триггеров ТМ2, которые можно назвать «D-триггерами, тактируемыми фронтом» или «синхронными D-триггерами».

Для того чтобы подчеркнуть различие между ними, приведем логику работы D-триггера, тактируемого фронтом импульса:

1) хранение информации осуществляется при подаче на вход С как лог. 0, так и лог. 1;

2) прямое прохождение сигнала на выход со входа D нет;

3) запоминается информация, имеющаяся на входе D перед фронтом импульса положительной полярности на входе С;

4) изменение информации на выходе может происходить только во

время фронта на входе С.

Микросхема ТМ8 (рис. 49) - регистр хранения информации, содержащий четыре синхронных D-триггера, по функционированию анало

гичных триггерам микросхем ТМ2. Сброс триггеров происходит при подаче лог. 0 на вход R, запись - по спаду импульса отрицательной полярности на входе С. Информация на входах D1 - D4 может меняться как при лог. 0, так и при лог. 1 на входе С, она важна лишь непосредственно перед изменением сигнала на входе С с лог. 0 на лог. 1. Микросхема ТМ9 - регистр хране ния информации, содержащий шесть D-триггеров, по функционированию аналогичных триггерам микросхем ТМ2 и ТМ8. Микросхема К155ИР1 (рис. 50) - четырехразрядный сдвигающий регистр, позволяет производить последовательную и параллельную запись информации в триггеры регистра, последовательное и параллельное считывание информации, сдвиг информации. Вход С1 микросхемы служит для подачи положительных тактовых импульсов, сдвигающих информацию, причем сдвиг происходит по спадам импульсов. При подаче положительного импульса на вход С2 по его спаду происходит запись в триггеры регистра информации, имеющейся на входах D1 - D4. Кроме того, есть управляющий вход EL. Запись со входов D1 - D4 может происходить лишь при наличии лог. 1 на входе EL, сдвиг - при наличии лог. 0. Для последовательной записи информации используется вход D0, запись происходит в режиме сдвига.

Наличие управляющего входа EL расширяет возможности использования микросхемы. Если соединить между собой входы С1 и С2, можно управлять сдвигом и записью, лишь изменяя логический уровень на входе EL. Можно соединить между собой входы С2 и EL, специального управляющего сигнала в этом случае не потребуется -сдвиг будет происходить при подаче импульсов на вход С1, запись -при подаче импульсов на С2. Если вход D1 подключить к выходу 2, D2 - к выходу 3, D3 - к выходу 4, а D4 использовать в качестве входа последовательной записи, то получится реверсивный сдвигающий регистр. При подаче импульсов на вход С1 будет происходить последовательная запись информации со входа D0 и сдвиг в сторону возрастания номеров выходов (сдвиг вправо). При подаче импульсов на вход С2 запись будет происходить со входа D4, сдвиг - в сторону уменьшения номеров выходов (сдвиг влево).